## **SRAM**

Dr. Jing Pang

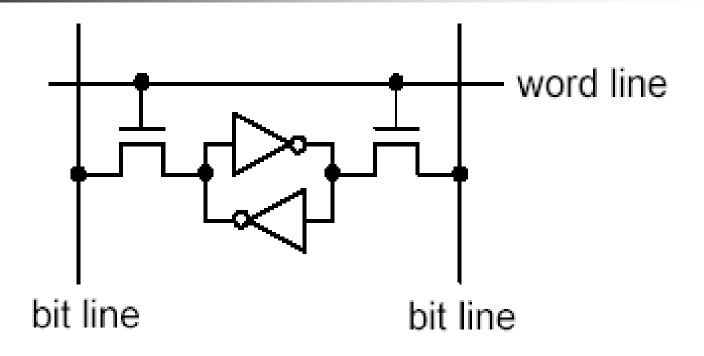

### **SRAM Cell**

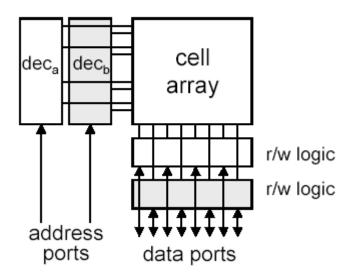

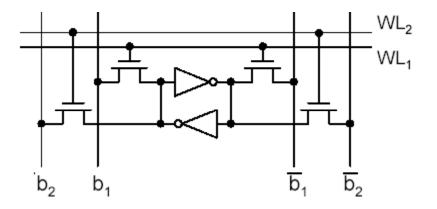

## **Dual-Port Memory**

Add decoder, another set of read/write logic, bits lines, word lines:

• Example cell: SRAM

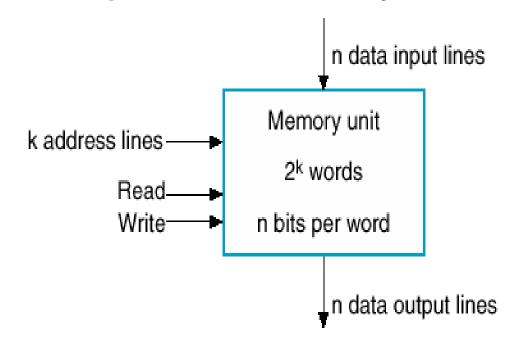

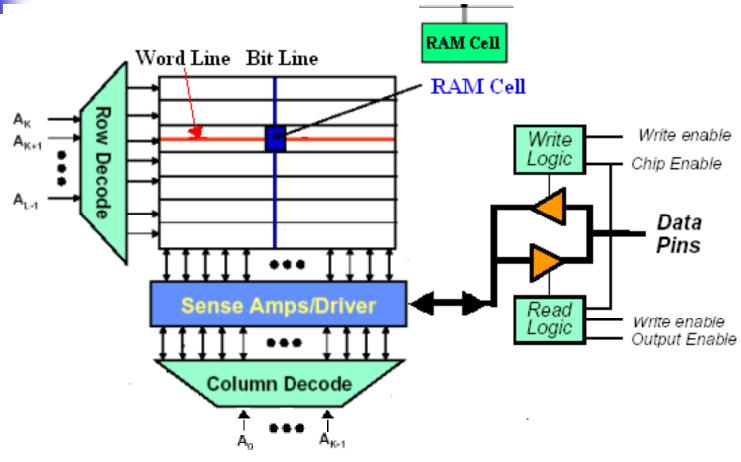

### Simple View of RAM

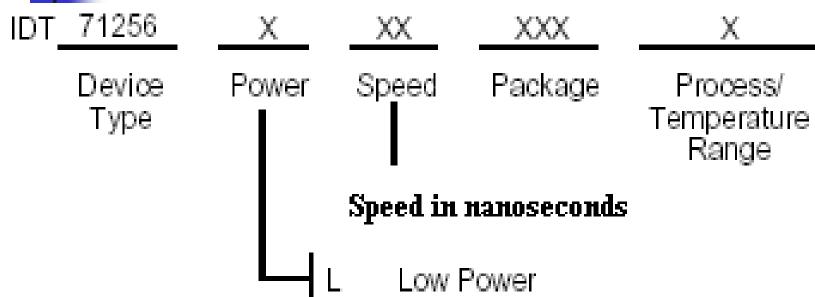

#### RAM Naming Convention

- Examples: 32 X 8, "32 by 8" => 32 8-bit words

### RAM Architecture

## 1K x 16 memory

#### 10 address lines and 16 data lines

#### Memory address

| Binary     | Decimal | Memory contents   |

|------------|---------|-------------------|

| 000000000  | 0       | 10110101 01011100 |

| 000000001  | 1       | 10101011 10001001 |

| 000000010  | 2       | 00001101 01000110 |

|            | •       | •                 |

|            | •       | •                 |

|            | •       | •                 |

|            | •       | •                 |

|            | •       | •                 |

| 1111111101 | 1021    | 10011101 00010101 |

| 1111111110 | 1022    | 00001101 00011110 |

| 1111111111 | 1023    | 11011110 00100100 |

| A14 🗆             | ď  |       | 28 | □Vcc              |

|-------------------|----|-------|----|-------------------|

| A <sub>12</sub> □ | 2  |       | 27 |                   |

| A7 🗆              | 3  |       | 26 | □ A <sub>13</sub> |

| A6 🗆              | 4  |       | 25 | □ A8              |

| A5 🗆              | 5  |       | 24 | $\square_{A_9}$   |

| A4 🗆              | 6  | DТ    | 23 | □ A <sub>11</sub> |

| Аз 🗆              | 7  | 71256 | 22 |                   |

| A2 🗆              | 8  |       | 21 | □ A10             |

| A1 □              | 9  |       | 20 | □ <del>CS</del>   |

| Ao 🗆              | 10 |       | 19 | □ I/O7            |

| I/O₀ □            | 11 |       | 18 | □ I/O6            |

| 1/0₁ □            | 12 |       | 17 | □ I/O5            |

| I/O2 □            | 13 |       | 16 | □ I/O4            |

| GND □             | 14 |       | 15 | □ I/O3            |

|                   |    |       |    |                   |

#### **Truth Table**

| WĒ | <u>cs</u> | ŌĒ | 1/0    | Function        |

|----|-----------|----|--------|-----------------|

| Х  | Н         | Χ  | High-Z | Standby         |

| Н  | L         | Н  | High-Z | Output Disabled |

| Н  | L         | L  | Dour   | Read Data       |

| L  | L         | Χ  | DN     | Write Data      |

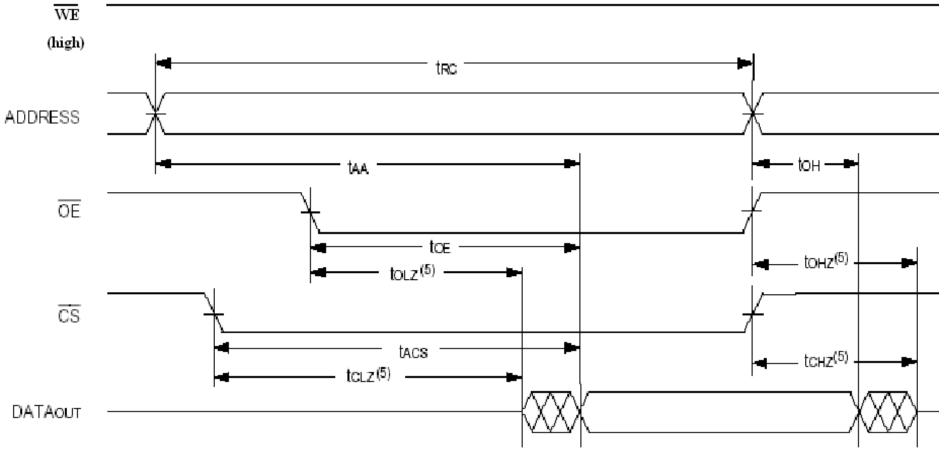

# Reading

- Steps

- Setup address lines

- Activate read line

- Data available after specified amount of time

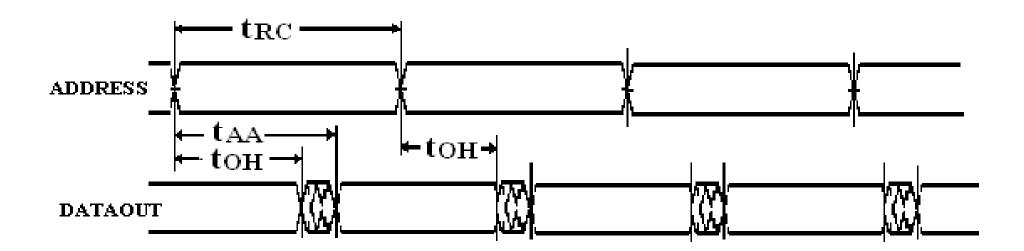

## Read Cycle

## Read Cycle

|        |                                 | 71256S55<br>71256L55 |      | 71256S70<br>71256L70 |      | 71256S85<br>71256L85 |      | 71256S100<br>71256L100 |      |

|--------|---------------------------------|----------------------|------|----------------------|------|----------------------|------|------------------------|------|

| Symbol | Parameter (ns)                  | Min.                 | Max. | Min.                 | Max. | Min.                 | Max. | Min.                   | Max. |

| tRC    | Read Cycle Time                 | 55                   |      | 70                   |      | 85                   |      | 100                    |      |

| taa    | Address Access Time             |                      | 55   |                      | 70   |                      | 85   |                        | 100  |

| tacs   | Chip Select Access Time         |                      | 55   |                      | 70   |                      | 85   |                        | 100  |

| taz    | Chip Select Time                | 5                    |      | 5                    |      | 5                    |      | 5                      |      |

| toE    | Output Enable to Output Valid   |                      | 25   | -                    | 30   |                      | 35   | -                      | 40   |

| toz    | Output Enable Time              | 0                    |      | 0                    |      | 0                    |      | 0                      |      |

| tон    | Output Hold from Address Change | 5                    |      | 5                    |      | 5                    |      | 5                      |      |

# Multiple Read

$$\overline{WE}$$

='1',  $\overline{CS}$ ='0',  $\overline{OE}$ ='0'

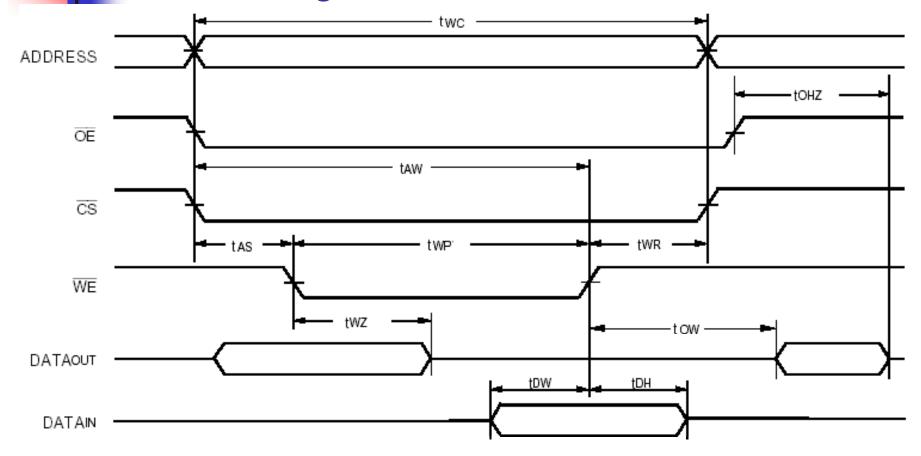

# Writing

- Sequence of steps

- Setup address lines

- Setup data lines

- Activate write line

## Write Cycle

## Write Cycle

|                            |                                | 71256S55<br>71256L55 |      | 71256S70<br>71256L70 |      | 71256S85<br>71256L85 |      | 71256S100<br>71256L100 |      |

|----------------------------|--------------------------------|----------------------|------|----------------------|------|----------------------|------|------------------------|------|

| Symbol                     | Parameter (ns)                 | Min.                 | Max. | Min.                 | Max. | Min.                 | Max. | Min.                   | Max. |

| $\mathbf{t}_{\mathrm{WC}}$ | Write Cycle Time               | 55                   |      | 70                   | _    | 85                   |      | 100                    | _    |

| tas                        | Address Setup Time             | 0                    |      | 0                    | _    | 0                    | _    | 0                      | _    |

| $t_{\mathrm{WP}}$          | Write Pulse Width              | 40                   |      | 45                   | _    | 50                   | _    | 55                     | _    |

| $t_{ m WR}$                | Address Hold Time              | 0                    |      | 0                    | _    | 0                    | _    | 0                      | _    |

| $t_{ m DW}$                | Data Setup Time                | 25                   |      | 30                   | _    | 35                   | _    | 40                     | _    |

| t <sub>DH</sub>            | Data Hold from Write Time (WE) | 0                    |      | 0                    | _    | 0                    | _    | 0                      | _    |